Laboranalytik und Produktzertifizierung

Analyse der Prozess- und Produktqualität, unsere Labore.

Um die vollständige Konformität der technischen Spezifikationen und Konstruktionseigenschaften von Leiterplatten mit immer strengeren Anforderungen und Qualitätsstandards zu gewährleisten, bedarf es geeigneter Instrumente.

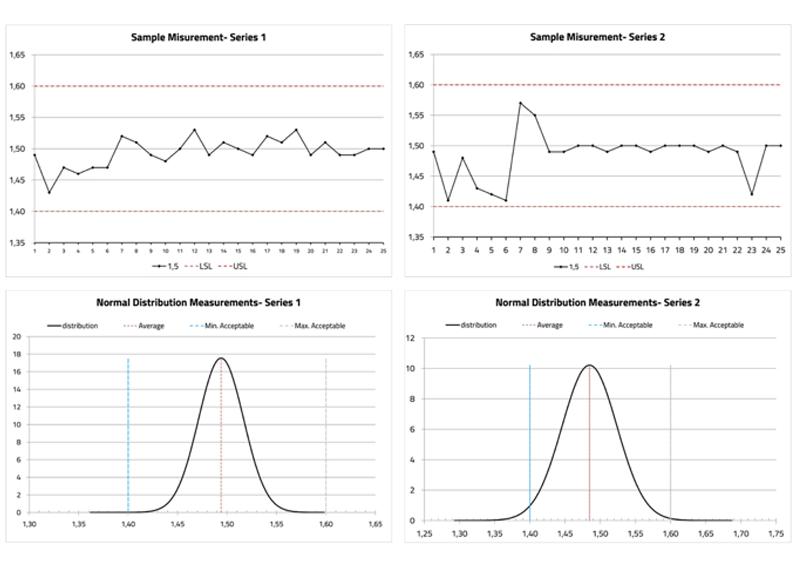

Insbesondere sind Instrumente notwendig, um die Statistische Prozesskontrolle (SPC) und die daraus folgende Analyse der Leiterplatten zu unterstützen.

Heute ist es unerlässlich, Kontrollen und Bewertungen durchzuführen, um die Konformität der Leiterplatten während des gesamten Lebenszyklus des Produkts, in dem sie eingebaut sind, unabhängig vom Anwendungsbereich und Marktsektor zu gewährleisten.

Der Miniaturisierungsprozess und die wachsenden Leistungsanforderungen an elektronische Produkte haben den Technologiegehalt und die Komplexität von Leiterplatten erhöht.

Es war daher notwendig, sich mit den fortschrittlichsten Labortechnologien auszustatten, um die Konformität gemäß den internationalen Standards bei der Herstellung elektronischer Produkte und gemäß den spezifischen Anforderungen des Endkunden zu gewährleisten.

Internationale Normen, vor allem die IPC-Normen, empfehlen insbesondere eine verstärkte Zusammenarbeit zwischen Designern (in der Regel als Vertreter des Endverbrauchers), Herstellern und Bestückern von Leiterplatten, um Schwachstellen des montierten Systems aus Leiterplatte und elektronischen Baugruppen (PCBA) und allgemeiner des Endprodukts zu minimieren.

Die Validierungstests von Leiterplatten sind hauptsächlich auf die IPC TM-650 Normen und auf die Standards zurückzuführen, die in sektorspezifischen Regelwerken wie MIL für den militärischen Bereich und ESA ECSS für Anwendungen im Raumfahrtsektor beschrieben sind.

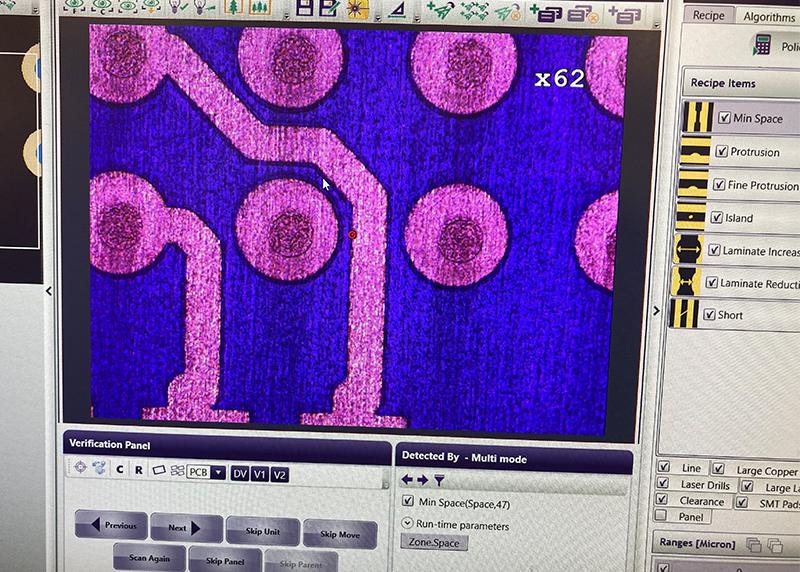

Schliffbilder dienen der Prüfung der inneren Merkmale

(d. h. der Dicke der Kupferschicht auf den Lochwänden und nicht der Qualität der Füllung mit Kupfer bei copper filling oder mit Epoxidharz bei Via-in-Pad und anderen Lösungen) und zur Bewertung der kritischsten Punkte wie der Ecken der PTH-Löcher und der Durchkontaktierungen oder des Restrings in der Nähe der Verbindungen zwischen Bohrung und Innenlagen.

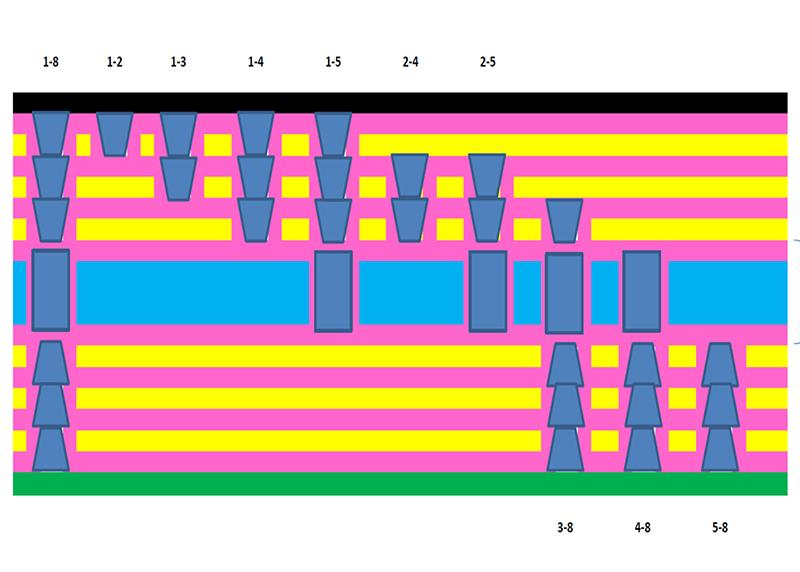

Ein weiterer grundlegender Aspekt ist die Prüfung des Stack-ups, insbesondere, aber nicht nur, bei impedanzkontrollierten Leiterplatten. Anhand des Schliffbilds können das Vorhandensein und die Dicke aller vorgesehenen Schichten sowie die Dicke des Basiskupfers der Innenlagen und nachfolgenden chemischen und elektrolytischen Kupferauflagen bewertet werden.

Die kontrollierten Impedanzen werden in der Entwicklungsphase der Leiterplatte von den Designern auf der Grundlage des für ihre Realisierung ausgewählten Materials berechnet und dann in der Machbarkeits- und Engineering-Phase auf der Grundlage des definitiven Materials erneut verifiziert und simuliert. Die Dielektrizitätskonstante des Basislaminats bestimmt zusammen mit der Dimensionierung der Leiterbahnen mit Impedanzkontrolle den Wert der kontrollierten Impedanzen.

Die Messung der Impedanzen kann mit in die Produktionsausrüstung eingesetzten repräsentativen Testcoupons erfolgen.

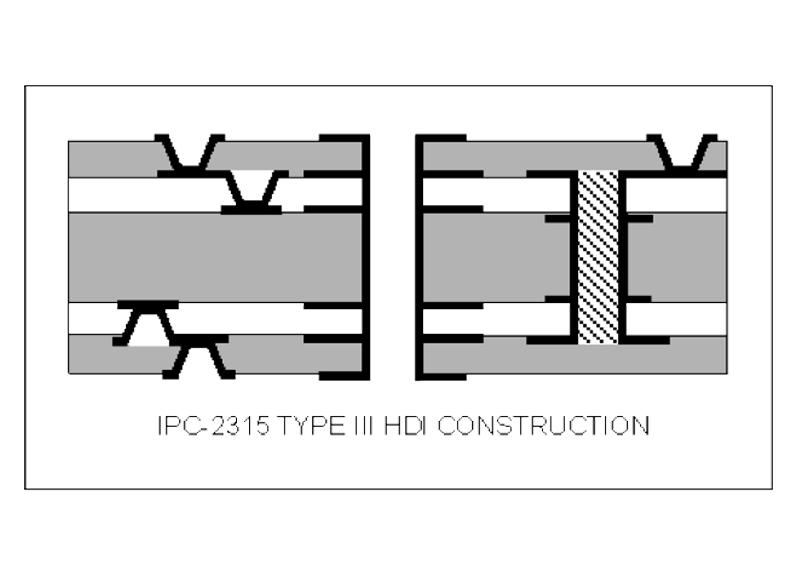

Die Notwendigkeit, Leiterplatten mit immer kleineren Abmessungen zu haben, hat die Designer gezwungen, die internen Verbindungen zu erhöhen und Hightech-Lösungen wie einzelne oder sequentielle Sacklochbohrungen (blind vias) oder vergrabene Durchkontaktierungen (buried vias) anzuwenden, um die verschiedenen Lagen miteinander zu verbinden.

Komplexere Strukturen mit zunehmender Bohrdichte machen Leiterplatten empfindlicher gegenüber thermischen Beanspruchungen, denen sie insbesondere bei den Lötverfahren elektronischer Bauteile ausgesetzt sind.

Aus diesem Grund sind thermische Belastungstests unerlässlich, um das Verhalten der Platinen und ihre Festigkeit während des Reflow-Lötprozesses im Ofen unmittelbar nach der Platzierung der mit Pick-and-Place-Geräten ausgeführten SMD-Bauteile zu simulieren.

Die Überprüfung der Metallisierungsbeständigkeit der PTH-Löcher erfolgt mit thermischen Belastungstests: Gemäß den IPC TM650-Standards werden 3 Belastungstests bei 288 °C (IPC TM 650 2.6.8) ausgeführt oder der Reflowprozess wird mit 6 Belastungstests bei 260 ° C simuliert (IPC TM650 2.6.27).

Zu den zerstörenden Prüfungen, die die Leiterplatte unbrauchbar machen und die oft notwendig sind, um deren durch die speziellen Herstellungsverfahren bedingten Merkmale zu untersuchen, kommen zerstörungsfreie Prüfungen hinzu.

Ein Beispiel ist die Röntgenfluoreszenz-Analyse (RFA) zur Bestimmung der Dicke von Endoberflächen (HASL, ENIG, ENEPIG, tin-lead Hot Oil reflow, Immersion Silver, Immersion Tin, iSiG,- Hard Gold).

Die Analyse der Dicke der Endoberfläche ermöglicht neben der Konformitätsprüfung der Leiterplatte auch die Kontrolle der Beschichtungsprozesse.

Oberflächendicken, die nicht den IPC-Normen entsprechen, können während des Lötprozesses der Bauteile zu verschiedenen Problemen führen.

Alle oben beschriebenen Analysen garantieren zusammen mit anderen von uns standardmäßig durchgeführten Prüfungen die Konformität der Leiterplatte und ihre langfristige Zuverlässigkeit.

Die Ergebnisse der Produktanalysen werden in den Dokumenten zusammengefasst, die üblicherweise zur Zertifizierung der Produktkonformität verwendet werden, wie z. B.: FAI Report, PPAP, Testberichte, die in Übereinstimmung mit den Normen ISO 9001, EN9100, IATF, ISO13485, ISO TS 22163 und ESA ECSS und nach spezifischen Kundenwünschen vorbereitet und zusammengestellt werden.

Wir garantieren die erstklassige Qualität Ihrer Leiterplatte, indem wir die Funktionalität des kompletten Gerätes mithilfe der besten Labortechnologien überprüfen.