La qualità viene prima di tutto nei circuiti stampati!

Per garantire il pieno rispetto delle specifiche tecniche e delle caratteristiche costruttive dei circuiti stampati secondo requisiti e standard qualitativi sempre più stringenti, risulta necessario dotarsi di strumenti adeguati.

Occorrono, in particolare, strumenti capaci di supportare l’analisi dei processi secondo tecniche di Controllo Statistico di Processo (SPC) e l’analisi dei circuiti stampati che ne derivano.

Oggi risulta imprescindibile garantire la conformità dei circuiti stampati per tutto il proprio ciclo di vita qualsiasi sia l’ambito di applicazione, dall’Aerospace & Defense al settore Automotive passando per quelli Ferroviario e Medicale fino a quello dell’Automazione Industriale.

Il processo di miniaturizzazione unito alle crescenti esigenze in termini di performance dei prodotti elettronici, hanno incrementato il contenuto tecnologico e la complessità dei circuiti stampati.

Si è così reso necessario dotarsi delle più avanzate tecnologie di laboratorio per accertarne la conformità sia secondo standard internazionali in uso nell’ambito della fabbricazione di prodotti elettronici sia secondo specifici requirements espressi dal cliente finale.

Gli standard internazionali in questione, primo tra tutti quello rappresentato dalle norme IPC, suggeriscono, in particolare, di sviluppare la collaborazione tra designers (rappresentanti del consumatore finale in genere), produttori e assemblatori di circuiti stampati per minimizzare le criticità del sistema assemblato costituito da circuito stampato e componenti elettronici (PCBA) e, più in generale, del prodotto finito.

I test di validazione dei circuiti stampati sono per lo più riconducibili alle norme IPC TM650 e agli standard descritti da normative specifiche di settore come le MIL, per il settore Militare, e le ECSS ESA per le applicazioni nel settore Spazio.

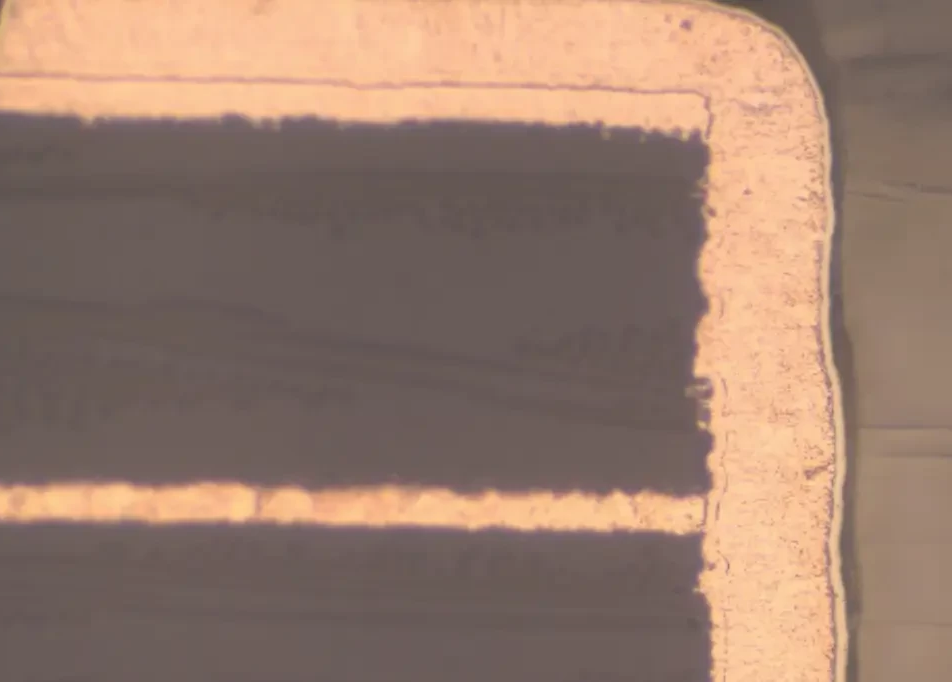

Anche la preparazione e la lettura delle microsezioni è normata dalle IPC.

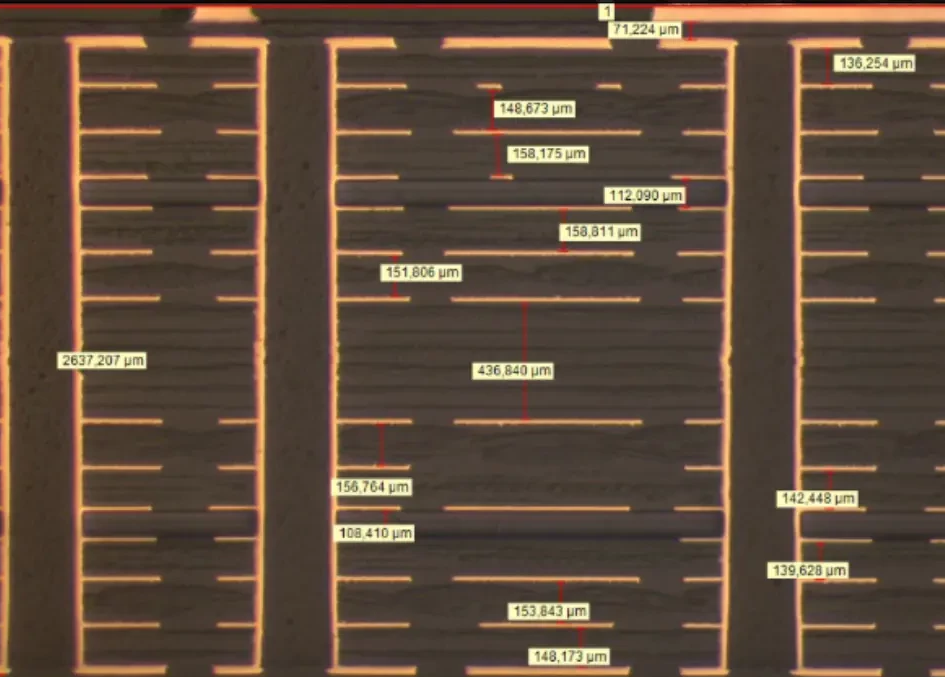

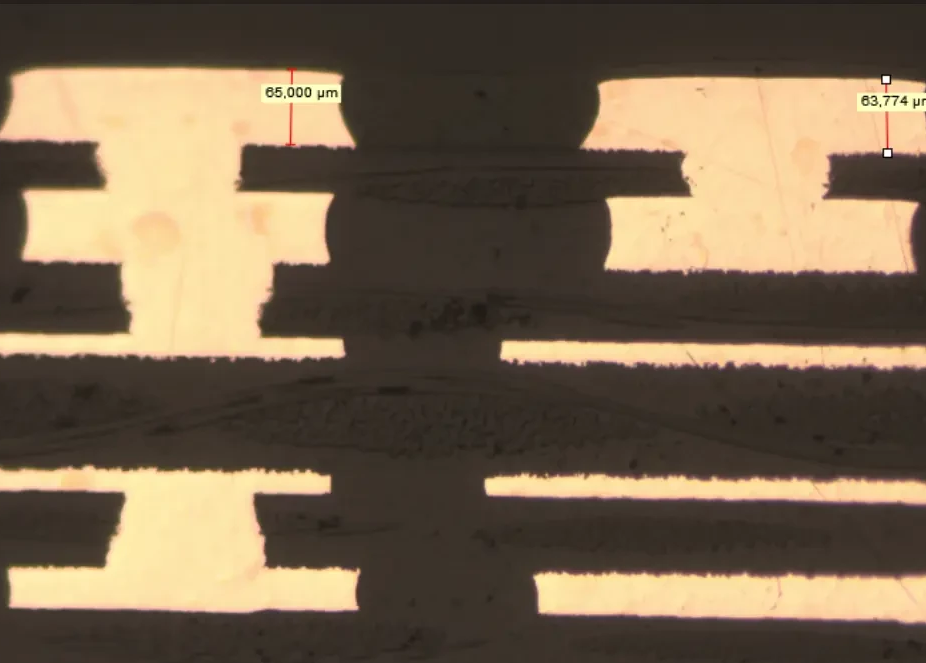

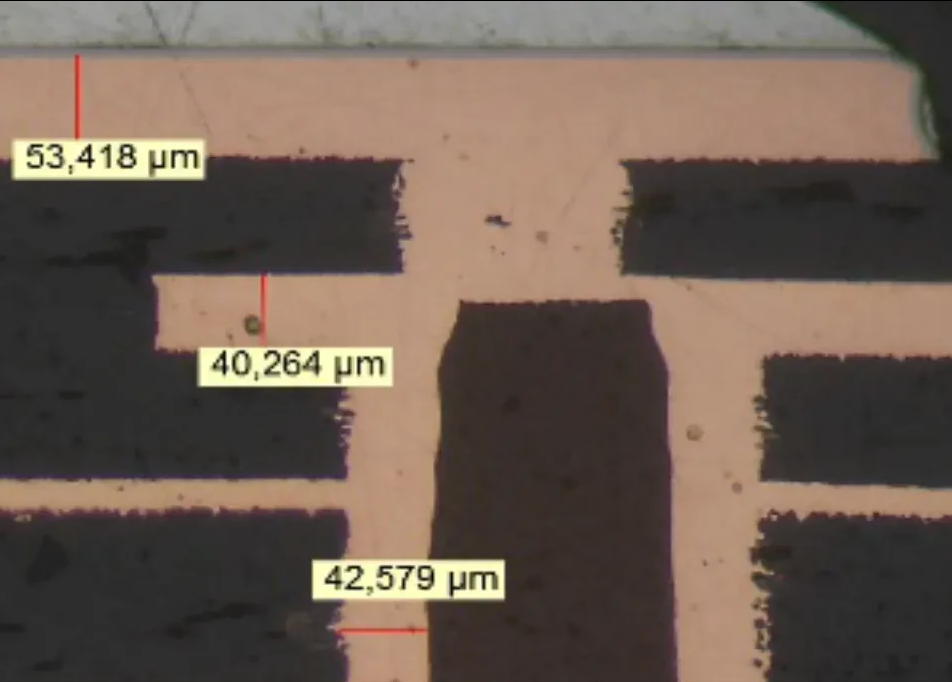

Le microsezioni sono utilizzate per la verifica delle caratteristiche interne (i.e. lo spessore del deposito di rame alle pareti dei fori piuttosto che la qualità del riempimento dei fori con rame, nel caso del copper filling, o di resina epossidica per lo più nel caso di soluzioni del tipo vias in pad e per molti altri casi) e per la valutazione dei punti più critici come i corner dei fori PTH e/o dei fori vias o dell’annular ring in prossimità delle interconnessioni tra foro ed innerlayers.

Un altro aspetto fondamentale è la verifica dello stack up di costruzione, soprattutto, ma non solo, per i circuiti con impedenze controllate. La microsezione consente di valutare la presenza e lo spessore di tutti gli strati previsti e permette inoltre di valutare lo spessore di rame di base degli innerlayers e dei successivi riporti di rame chimico e rame elettrolitico.

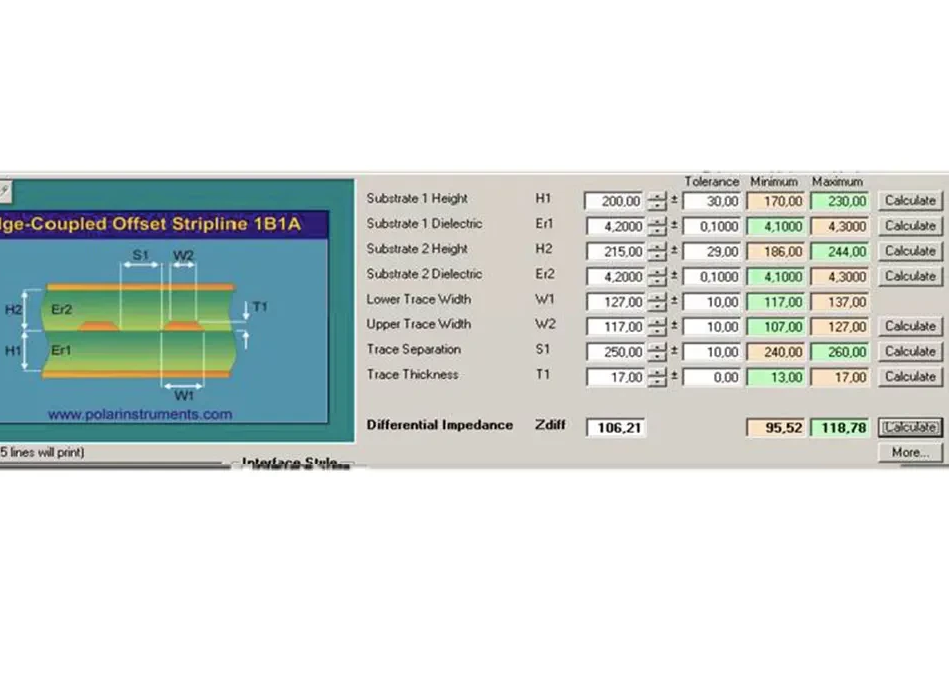

Le impedenze controllate vengono calcolate in fase sviluppo del circuito stampato da parte dei designer, sulla base del materiale scelto per la relativa realizzazione, e poi riverificate e simulate in fase di fattibilità e di ingegnierizzazione, sulla base del materiale definitivamente condiviso con lo stesso designer. La costante dielettrica del laminato di base assieme al dimensionamento delle piste ad impedenza determinano il valore delle impedenze controllate.

E’ possibile effettuare la misurazione delle impedenze tramite appositi test coupon inseriti all’interno dell’attrezzatura di produzione per garantire la massima rappresentatività degli stessi nei confronti del PCB.

La necessità di avere schede con dimensioni sempre più contenute ha costretto i designer ad aumentare le interconnessioni interne e adottare soluzioni più tecnologicamente avanzate come fori ciechi (blind vias) singoli o sequenziali, fori Interrati (buried vias) per permettere ai vari layers di essere connessi tra loro.

Strutture più complesse con densità di forature sempre maggiori rendono i circuiti stampati maggiormente sensibili alle sollecitazioni termiche che subiscono durante i processi di saldatura dei componenti elettronici.

Per questo motivo i test di stress termico risultano fondamentali per simulare il comportamento delle schede e la loro solidità durante il processo di saldatura in forno di reflow immediatamente successivo al posizionamento della componentistica SMD operata con macchine pick & place.

Per verificare la resistenza della metallizzazione dei fori PTH vengono praticati stress termici: in accordo agli standard IPC TM650, sono praticati con 3 stress a 288°C (IPC TM 650 2.6.8), oppure viene simulato il processo di rifusione con 6 stress a 260°C (IPC TM650 2.6.27).

Alle analisi distruttive, quelle che cioè rendono la scheda inutilizzabile e che si rendono spesso necessarie per indagare le caratteristiche che il circuito stampato deriva dai processi speciali di fabbricazione, si aggiungono le analisi non distruttive.

Un esempio ne è l’analisi X-Ray Fluorescence Spectroscopy (XRF) per determinare lo spessore delle finiture superficiali (HASL, ENIG, ENEPIG, tin-lead Hot Oil reflow, Immersion Silver, Immersion Tin, iSiG,- Hard Gold).

L’analisi dello spessore della finitura superficiale, oltre che essere un controllo di processo, risulta fondamentale anche per garantire la conformità della scheda. Spessori di finitura non conformi agli standard IPC, possono infatti creare diverse problematiche durante il processo di saldatura dei componenti.

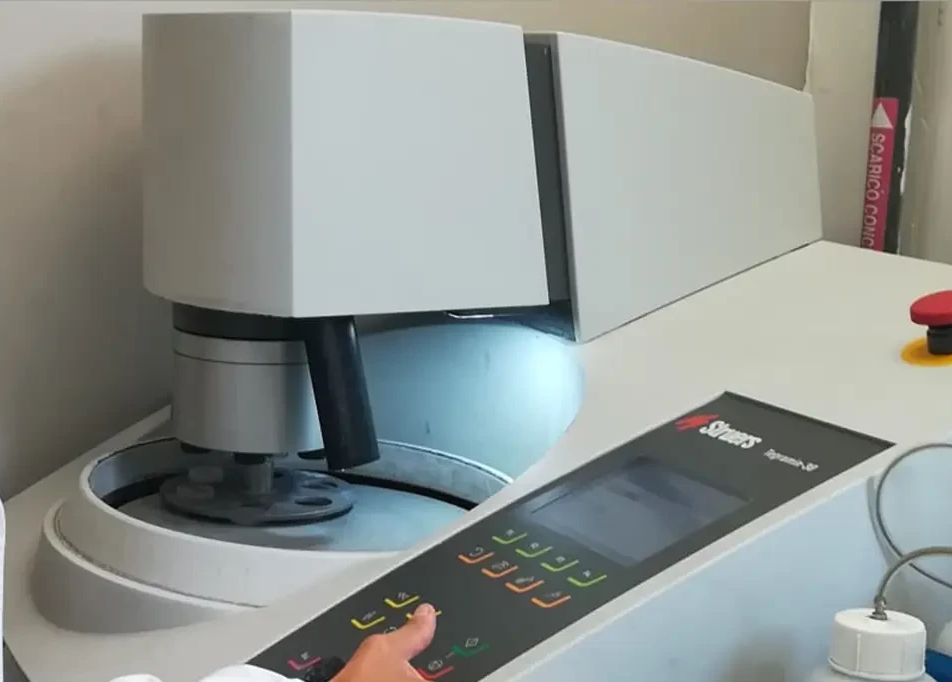

Per la verifica della qualità della finitura superficiale dei circuiti stampati, e per evitare problemi di qualità della saldatura dei componenti elettronici e di adesione del conformal coating, si utilizza la verifica di contaminazione ionica.

Questo test è realizzato tramite un contaminometro, attraverso il quale è possibile estrarre e misurare, sotto forma di NaCl equivalente, la quantità di alogenuri (sali di Cloro, Bromo, Fluoro, Cromo) presenti sulla superficie del circuito stampato. Questo metodo è conosciuto con il nome di Resistivity of Solvent Extract (ROSE).

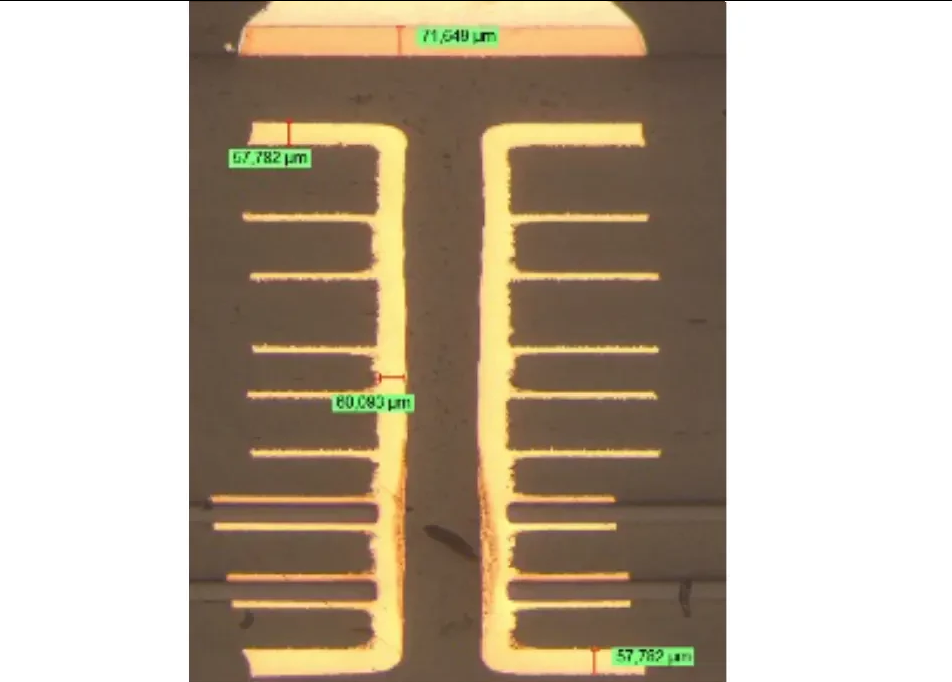

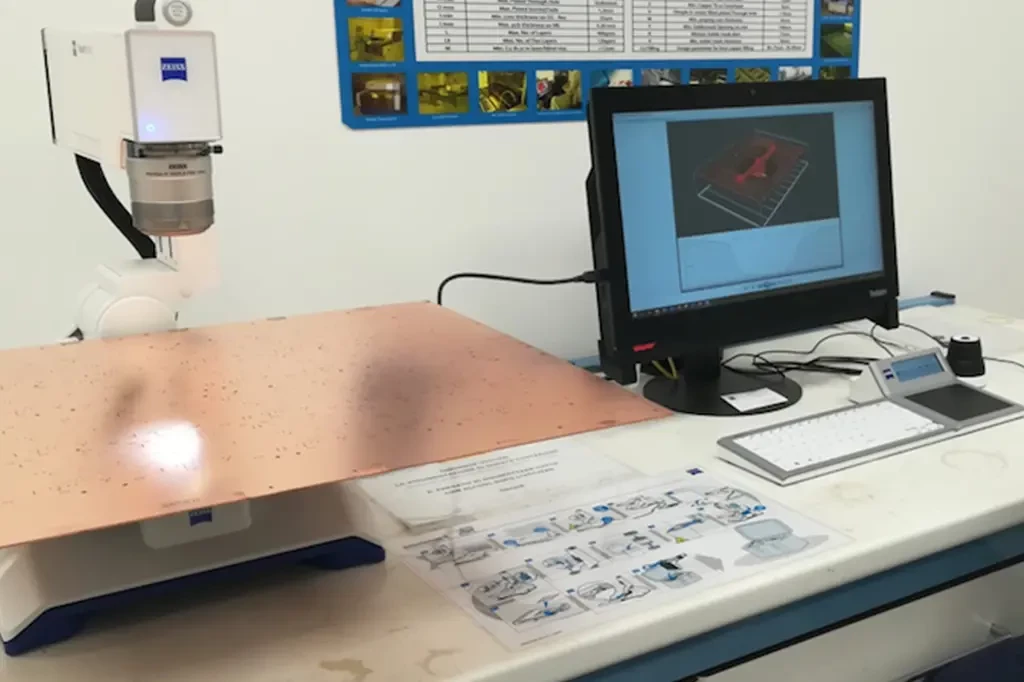

Le recenti tecnologie ispettive hanno inoltre permesso lo sviluppo di altre verifiche non distruttive 3D, tra le quali quelle di rugosità superficiale, del dimple di fori filled, di profondità delle cavity, di sottoincisione di piste RF, e, ancora, quelle di qualità dei fori ciechi ottenuti per foratura laser o foratura meccanica e dei fori lavorati con backdrilling. In questo secondo caso, in particolare, l’analisi al microscopio 3D permette di evitare di ricorrere alla microsezione semplificando l’attività di verifica e riducendone sensibilmente i tempi.

Questo, oltre che accelerare le verifiche in process e di conseguenza aumentare il campionamento di esemplari da verificare, permette anche di poter dare supporto al cliente anche in fase post assemblaggio con verifiche 3D della scheda assemblata.

Tutte le analisi sopradescritte, assieme ad altre di cui parleremo in seguito, garantiscono la conformità del circuito stampato e la sua affidabilità nel tempo.

Concludiamo segnalando che i risultati delle analisi di prodotto vengono raccolte nei documenti comunemente utilizzati per certificare la conformità di prodotto quali: FAI Report, PPAP, Test Report predisposti e compilati in accordo agli standard EN9100, IATF, ISO13485, ISO TS 22163 e ESA ECSS e secondo eventuali richieste specifiche dei clienti.

Cistelaier, TECHCI ed EPN Electroprint – le tre società produttrici di circuiti stampati appartenenti alla Divisione PCB del Gruppo Finmasi – garantiscono la migliore qualità controllando i propri processi e prodotti servendosi delle migliori tecnologie di laboratorio.